## Proceedings of the

# 15th International Conference on Real-Time and Network Systems

# **RTNS'07**

LORIA, Nancy, France 29-30 March 2007

http://rtns07.irisa.fr

## **Table of contents**

# 15th conference on Real-Time and Network Systems RTNS'07

| Message from the conference chairs                                                                             |

|----------------------------------------------------------------------------------------------------------------|

| Organizing committee                                                                                           |

| Program committee                                                                                              |

| Reviewers                                                                                                      |

| Keynote presentation                                                                                           |

| Implementation and Challenging Issues of Flash-Memory Storage Systems                                          |

| Formal methods                                                                                                 |

| The Timed Abstract State Machine Language: An Executable Specification Language for Reactive Real-Time Systems |

| Martin Ouimet, Massachusetts Institute of Technology, USA                                                      |

| Kristina Lundqvist, Massachusetts Institute of Technology, USA                                                 |

| Mikael Nolin, Maelardalen University, Sweden                                                                   |

| Extended Real-Time LOTOS for Preemptive Systems Verification                                                   |

| Tarek Sadani, LAAS-CNRS / Ensica, France                                                                       |

| Pierre de Saqui-Sannes, LAAS-CNRS / Ensica, France                                                             |

| Jean-Pierre Courtiat, LAAS-CNRS, France                                                                        |

| Generation of Tests for Real-time Systems with Test Purposes                                                   |

| Sebastien Salva, LIMOS, France                                                                                 |

| Patrice Laurençot, LIMOS, France                                                                               |

| Architectures and worst-case execution time estimation                                                         |

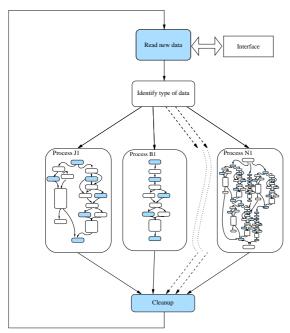

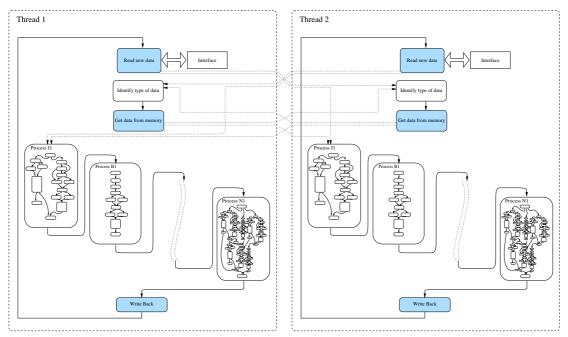

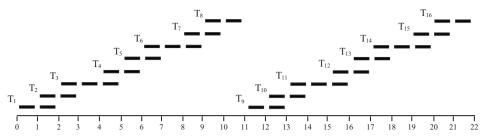

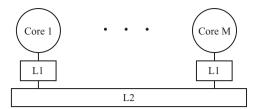

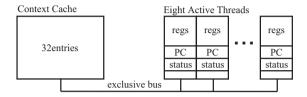

| Predictable Performance on Multithreaded Architectures for Streaming Protocol Processing 47                    |

| Matthias Ivers, Institut für Datentechnik und Kommunikationsnetze, Germany                                     |

| Bhavani Janarthanan, Institut für Datentechnik und Kommunikationsnetze, Germany                                |

| Rolf Ernst, Institut für Datentechnik und Kommunikationsnetze, Germany                                         |

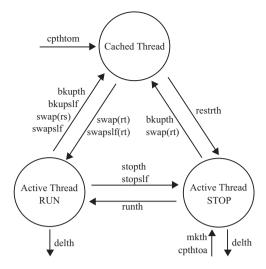

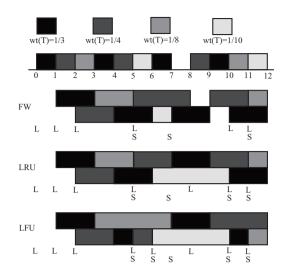

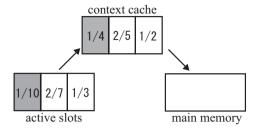

| A Context Cache Replacement Algorithm for Pfair Scheduling                                                     |

| Kenji Funaoka, Keio University, Japan                                                                          |

| Shinpei Kato, Keio University, Japan                                                                           |

| Nobuyuki Yamasaki, Keio University, Japan                                                                      |

| Exact Cache Changetonization by Experimental Baraneton Entraction                                              |

| Exact Cache Characterization by Experimental Parameter Extraction                                              |

| Tobias John, Chemnitz University of Technology, Germany<br>Robert Baumgartl, Chemnitz University of Technology, Germany                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Towards Predictable, High-Performance Memory Hierarchies in Fixed-Priority Preemptive  Multitasking Real-Time Systems                               |

| On the Sensitivity of WCET Estimates to the Variability of Basic Blocks Execution Times                                                             |

| Scheduling 1                                                                                                                                        |

| Efficient Computation of Response Time bounds under Fixed-Priority Scheduling                                                                       |

| Approximate Feasibility Analysis and Response-Time Bounds of Static-Priority Tasks with Release  Jitters                                            |

| Nathan Fisher, University of North Carolina, Chapel Hill, USA                                                                                       |

| Schedulability Analysis using Exact Number of Preemptions and no Idle Time for Real-Time Systems with Precedence and Strict Periodicity Constraints |

| Algorithm and Complexity for the Global Scheduling of Sporadic Tasks on Multiprocessors with  Work-Limited Parallelism                              |

| Scheduling 2                                                                                                                                        |

| Schedulability Analysis of OSEK/VDX Applications                                                                                                    |

| Improvement of the Configuration and the Analysis of Posix 1003.1b Scheduling                                                                       |

| An Extended Scheduling Protocol for the Enhancement of RTDBSs Performances                                                                          |

Samy Semghouni, Laboratoire Informatique L.I.T.I.S antenne du Havre, France Bruno Sadeg, Laboratoire Informatique L.I.T.I.S antenne du Havre, France Laurent Amanton, Laboratoire Informatique L.I.T.I.S antenne du Havre, France Alexandre Berred, Laboratoire de Mathématiques Appliquées du Havre, France

### **Scheduling and control**

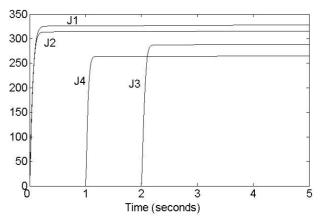

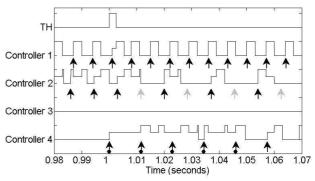

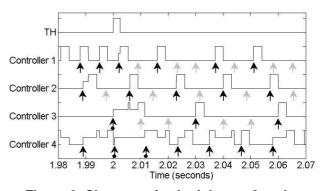

| Comparative Assessment and Evaluation of Jitter Control Methods                                                                                                                                                                                          | 163   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Reducing Delay and Jitter in Software Control Systems                                                                                                                                                                                                    | 173   |

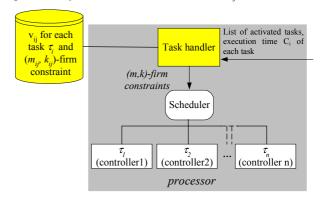

| Task Handler Based on (m,k)-firm Constraint Model for Managing a Set of Real-Time Controller Ning Jia, LORIA - University of Nancy, France YeQiong Song, LORIA - University of Nancy, France Francoise Simonot-Lion, LORIA - University of Nancy, France | rs183 |

| Networks and distributed systems                                                                                                                                                                                                                         |       |

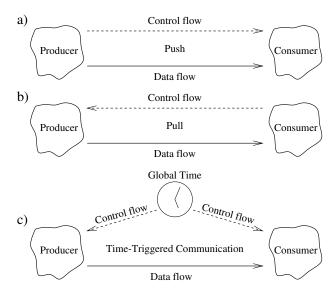

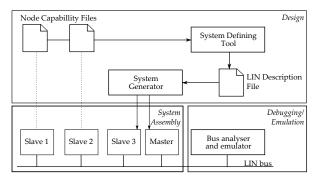

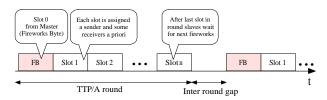

| Interface Design for Real-Time Smart Transducer Networks - Examining COSMIC, LIN, and TT as Case Study                                                                                                                                                   |       |

| Delay-Bounded Medium Access for Unidirectional Wireless Links                                                                                                                                                                                            | 205   |

| Tolerating Arbitrary Failures in a Master-Slave Clock-Rate Correction Mechanism for Time-<br>Triggered Fault-Tolerant Distributed Systems with Atomic Broadcast                                                                                          | 215   |

| Exploiting Slack for Scheduling Dependent, Distributable Real-Time Threads in Unreliable Networks                                                                                                                                                        | 225   |

## Message from the conference chairs

**RTNS'07**

It is our great pleasure to welcome you to the fifteenth Conference on Real-Time and Network Systems (RTNS'07) in Nancy, France. The primary purpose of RTNS is to provide the participants, academic researchers or practitioners, with a forum to disseminate their work and discuss emerging lines of research in the area of real-time and network systems: real-time system design and analysis, infrastructure and hardware for real-time systems, software technologies and applications.

The first thirteenth issues of the conference were held within the "Real Time Systems" trade show in Paris (at first, Palais des Congrès Porte Maillot, then Paris Expo, porte de Versailles). In 2005, it was decided to make the conference independent of the exhibition, emphasize the role of Systems on Networks (hence the transformation of the name from RTS to RTNS), and switch to English as the official language of the conference.

In response to the call for papers, 42 papers were submitted, among which 22 were selected by the international Program Committee. The presentation are organized in 6 sessions covering all major aspects of real-time systems: task scheduling (2 sessions), scheduling and control, formal methods, architecture and worst-case execution time estimation, real-time networks and distributed systems. In addition to the contributed papers, the RTNS technical program has the privilege to include a keynote talk by Professor Tei-Wei Kuo, from the National Taiwan University, who will share his views on the challenging issues raised by the use of flash-memory storage systems in embedded real-time systems. Furthermore, the second edition of the "Junior Researcher Workshop on Real-Time Computing" is held in conjunction with RTNS, and is a good opportunity for young researchers to present and get feedback on their ongoing work in a relaxed and stimulating atmosphere. All these presentations will provide an excellent snapshot of the current research results and directions in the area of real-time systems, and will certainly make RTNS a successful event.

Credit for the quality of the program is of course to be given to the authors who submitted high-quality papers and the program committee members and external referees who gave their time and offer their expertise to provide excellent reviews (at least three per paper). We are sincerely grateful to all of them.

RTNS'07 would not be possible without the generous contribution of many volunteers and institutions. First, we would like to express our sincere gratitude to our sponsors for their financial support: Conseil Général de Meuthe et Moselle, Conseil Régional de Lorraine, Communauté Urbaine du Grand Nancy, Université Henri Poincaré, Institut National Polytechnique de Lorraine and LORIA and INRIA Lorraine. We are thankful to Pascal Mary for authorizing us to use his nice picture of "place Stanislas" for the proceedings and web site (many others are available at <a href="www.laplusbelleplacedumonde.com">www.laplusbelleplacedumonde.com</a>). Finally, we are most grateful to the local organizing committee that helped to organize the conference. Let us hope for a bright future in the RTNS conference series!

Nicolas Navet, *INRIA-Loria, Nancy, France* Françoise Simonot-Lion, *LORIA-INPL, Nancy, France* General co-chairs

Isabelle Puaut, *University of Rennes / IRISA*, *France* Program chair

## **Organizing Committee**

**RTNS'07**

#### **General co-chairs**

Nicolas Navet, *INRIA-Loria, Nancy, France* Françoise Simonot-Lion, *LORIA-INPL, Nancy, France*

#### Program chair

Isabelle Puaut, *University of Rennes – IRISA*, *Rennes*, *France*

#### Junior workshop on real-time systems

Liliana Cucu, LORIA-INPL, Nancy, France

#### **Local arrangements**

Laurence Benini, INRIA, France

Najet Boughanmi, INRIA-Loria, France

Anne-Lise Charbonnier, INRIA, France

Liliana Cucu, LORIA-INPL, Nancy, France

Jean-François Deverge, IRISA, Rennes, France

Mathieu Grenier, INRIA-Loria, France

Christophe Païs, IRISA, Rennes, France

Xavier Rebeuf, LORIA-INPL, France

Olivier Zendra, INRIA-Loria, France

## **Program Committee**

#### **RTNS'07**

Sanjoy Baruah, University of North Carolina, USA Guillem Bernat, University of York, UK Enrico Bini, Scuola Superiore Sant'Anna, Pisa, Italy Alfons Crespo, Polytechnic University of Valencia, Spain Jean-Dominique Decotignie, EPFL, Lausanne, Switzerland Anne-Marie Déplanche, IRCCyN, Nantes, France Jose. A. Fonseca, University of Aveiro, Portugal Josep M. Fuertes, Technical University of Catalonia, Spain Joel Goossens, ULB, Brussels, Belgium Guy Juanole, LAAS, Toulouse, France Joerg Kaiser, University of Magdeburg, Germany Raimund Kirner, TU Vienna, Austria Tei-Wei Kuo, National Taiwan University, Taiwan Lucia Lo Bello, University of Catania, Italy Zoubir Mammeri, IRIT/UPS Toulouse, France Philippe Marquet, INRIA/LIFL, Lille, France Pascale Minet, INRIA-Rocquencourt, France Nicolas Navet, INRIA-Loria, Nancy, France Nimal Nissanke, London South Bank University, UK Mikael Nolin, Mälardalen University, Sweden Marc Pouzet, Université Paris Sud-LRI, France Pascal Richard, LISI / Poitiers, France Guillermo Rodríguez-Navas, University of Balearic Islands, Palma de Mallorca, Spain Bruno Sadeg, LITIS - University of Le Havre, France Maryline Silly-Chetto, IRCCyN, Nantes, France Daniel Simon, INRIA-Rhônes Alpes, France Françoise Simonot-Lion, LORIA-INPL, Nancy, France Eduardo Tovar, Polytechnic Institute of Porto, Portugal Yvon Trinquet, IRCCyN, Nantes, France Francisco Vasques, University of Porto, Portugal François Vernadat, LAAS, Toulouse, France Laurence T. Yang, St. Francis Xavier University, Canada

### **Reviewers**

#### **RTNS'07**

Tei-Wei Kuo Slim Abdellatif Bjorn Andersson Didier Lime Patricia Balbastre Jian-Hong Lin Lucia Lo Bello Sanjoy Baruah Mongi BenGaïd Zoubir Mammeri Guillem Bernat Philippe Marquet Marko Bertogna Pascale Minet Ricardo Moraes Enrico Bini Alexandre Mota Hadrien Cambazard Chien-Wie Chen Nicolas Navet Annie Choquet-Geniet Nimal Nissanke Yuan-Sheng Chu Mikael Nolin Michele Cirinei Harald Paulitsch Marc Pouzet Alfons Crespo Peter Puschner Jean-Dominique Decotignie Anne-Marie Déplanche Pascal Richard Andreas Ermedahl Bernhard Rieder Sébastien Faucou Guillermo Rodríguez-Navas Mamoun Filali Bruno Sadeg Jose A. Fonseca Michael Schulze Josep M. Fuertes Maryline Silly-Chetto Joel Goossens **Daniel Simon Emmanuel Grolleau** Françoise Simonot-Lion Pierre-Emmanuel Hladik Klaus Steinhammer Ping-Yi Hsu Eduardo Tovar Guy Juanole Yvon Trinquet Joerg Kaiser Francisco Vasques Thomas Kiebel François Vernadat Raimund Kirner Ingomar Wenzel Anis Koubaa Laurence T. Yang

## **Keynote presentation**

**RTNS'07**

# **Implementation and Challenging Issues of Flash-Memory Storage Systems**

#### Tei-Wei Kuo

#### National Taiwan University

Flash memory is widely adopted in the implementations of storage systems, due to its nature in excellent performance, good power efficiency, and superb vibration tolerance. However, engineers face tremendous challenges in system implementations, especially when the capacity of flash memory is expected to increase significantly in the coming years. This talk will address the implementation issues of flash-memory storage systems, such as performance and management overheads. Summary on existing solutions will be presented, and future challenges will also be addressed.

Prof. Tei-Wei Kuo received the B.S.E. degree in Computer Science and Information Engineering from National Taiwan University in Taipei, Taiwan, ROC, in 1986. He received the M.S. and Ph.D. degrees in Computer Sciences from the University of Texas at Austin in 1990 and 1994, respectively. He is currently a Professor and the Chairman of the Department of Computer Science and Information Engineering, National Taiwan University. Since February 2006, he also serves as a Deputy Dean of the National Taiwan University. His research interests include embedded systems, real-

time operating systems, and real-time database systems. He has over 140 technical papers published or been accepted in journals and conferences and a number of patents. Prof. Kuo works closely with the industry and serves as a review committee member of several government agencies and research/development institutes in Taiwan.

Dr. Kuo serves as the Program Chair of IEEE Real-Time Systems Symposium (RTSS) in 2007 and a Program Co-Chair of the IEEE Real-Time Technology and Applications Symposium (RTAS) in 2001. He is also an Associate Editor of several journals, such as the Journal of Real-Time Systems (since 1998) and IEEE Transactions on Industrial Informatics (since 2007). Dr. Kuo also serves as the Steering Committee Chair of IEEE International Conference on Embedded and Real-Time Computing Systems and Applications (RTCSA) since 2005. He is an Executive Committee member of the IEEE Technical Committee on Real-Time Systems (TC-RTS) since 2005. Dr. Kuo received several prestigious research awards in Taiwan, including the Distinguished Research Award from the ROC National Science Council in 2003, and the ROC Ten Outstanding Young Persons Award in 2004 in the category of scientific research and development.

# Formal methods

## The Timed Abstract State Machine Language: An Executable Specification Language for Reactive Real-Time Systems

Martin Ouimet, Kristina Lundqvist, and Mikael Nolin Embedded Systems Laboratory Massachusetts Institute of Technology Cambridge, MA, 02139, USA {mouimet, kristina}@mit.edu, mikael.nolin@mdh.se

#### **Abstract**

We present a novel language for specifying real-time systems. The language addresses a key challenge in the design and analysis of real-time systems, namely the integration of functional and non-functional properties into a single specification language. The non-functional properties that can be expressed in the language include timing behavior and resource consumption. The language enables the creation of executable specifications with welldefined execution semantics, abstraction mechanisms, and composition semantics. The language is based on the theory of abstract state machines. Extensions to the theory of abstract state machines are presented to enable the explicit specification of non-functional properties alongside functional properties. The theory is also extended to define the execution semantics for the hierarchical and parallel composition of specifications. The features of the specification language are demonstrated using a light switch example and the Production Cell case study.

#### 1 Introduction

The benefits and drawbacks of using formal methods have been documented heavily [10, 13]. Cited benefits include the detection of defects early in the engineering cycle, precise and concise specifications, and automated analysis [29]. Cited drawbacks include the heavy use of arcane mathematical notations, the lack of scalability of most methods, and the large investment typically required to use formal methods [13]. Besides the negative connotation that the term "formal methods" has taken in some circles, the benefits of unambiguous specifications and automated analysis during the early phases of the lifecycle have been generally accepted [5].

In the design and development of reactive real-time systems, the design and specification problem is more challenging than for traditional interactive systems because both functional behavior and non-functional behavior are part of the system's utility and must be specified precisely and concisely [9]. Furthermore, the specification and analysis of system designs is often performed at various levels of abstraction [17]. For example, the non-functional properties of system architectures can be specified and analyzed using an Architecture Description Language (ADL) such as the Society of Automotive Engineers' Architecture Analysis and Design Language (AADL) [28]. At the software application level, functional behavior can be specified and analyzed using statetransition systems such as finite state automata [18] or Petri nets [11]. Timing behavior can be specified and analyzed at either level using special purpose languages such as real-time logic or through specialized methods such as rate-monotonic analysis [12]. The need for multiple languages to specify and analyze system behavior can be expensive and error-prone because there is no formal connection between the different specifications resulting from the use of multiple languages [17]. This situation leads to redundant specifications that may not be consistent with one another.

This paper introduces the Timed Abstract State Machine (TASM) specification language, a novel specification language that removes the need to use many other specification languages. More specifically, TASM incorporates the specification of functional and non-functional behavior into a unified formalism. Furthermore, TASM is based on the theory of abstract state machines, a method for system design that can be applied at various levels of abstraction [8]. The TASM language has formal semantics, which makes its meaning precise and enables executable specifications.

The motivations and benefits of using Abstract State Machines (ASM), formerly known as evolving algebras, for hardware and software design have been documented in [6]. On the practical-side, ASMs have been used successfully on a wide range of applications, ranging from hardware-software systems to high-level system design [8]. Furthermore, there is enough evidence to believe that ASMs could provide a *literate* specification language, that is, a language that is understandable and usable without extensive mathematical training [13].

The anecdotal evidence supporting the success of the ASM method [6] suggests that tailoring the formalism to the area of reactive real-time systems could achieve similar benefits. The work presented in this paper extends the ASM formalism to make it amenable to real-time system specification. More specifically, the ASM formalism is extended to enable the explicit specification of timing behavior and resource consumption behavior. The resulting specification language, The Timed Abstract State Machine (TASM) language enables the specification of functional and non-functional properties into a unified formalism. The TASM language provides executable specifications that can express both sequential and concurrent behavior.

This paper is divided into five sections in addition to this Introduction. The following section situates the present work in relation to other research on similar topics. The abstract state machine formalism is introduced in section 3. Section 4 explains the modifications that have been made to the presented formalism to make it amenable to specification of real-time systems. Each extension is illustrated through the use of a light switch example. Section 5 provides a more substantial example of the feature of the TASM language through the production cell case study [19]. Finally, the Conclusion and Future Work section, Section 6, summarizes the contributions of the research and explains the additions that are to come in future development.

#### 2 Related Work

In the academic community, there are numerous mathematical formalisms that have been proposed for specifying and analyzing real-time systems. The formalism presented in this paper is similar to the timed transition systems formalism presented in [16]. The two formalisms differ in the concurrency semantics since timed transition systems adopt an interleaving model whereas ASM theory adopts a general model of concurrency [8]. The most popular formalisms developed in academia can be classified into three main families: automata, process algebra, and Petri nets [3].

In the automata family, timed automata are finite state automata extended with real-valued clocks and communication channels. The formalism has been used on a variety of applications and is the formalism used in the model checker UPPAAL [18]. The formalism is well-suited for analysis by model-checking, but the lack of structuring mechanisms makes abstraction and encapsulation difficult to achieve [4]. Statecharts and the associated tool STATE-MATE [15] augment automata with structuring mechanisms (superstates). Statecharts also include time concepts through the use of delays and timers.

In the Petri net family, a large number of variations on the traditional Petri net model have been developed, including various models of time [11]. Non-determinism is an essential part of Petri nets, which makes Petri net unsuitable for the specification of safety-critical real-time systems where predictability is of highest importance [4].

In the process algebra family, various offsprings of Communicating Sequential Processes (CSP) [2] and the Calculus of Communicating Systems (CCS) [20] have been defined, including multiple versions of timed process algebra [2]. However, in this formalism, it is difficult to express non-functional properties other than time (e.g., resource consumption). Timed LOTOS (ET-LOTOS) [2] is an example of a language from the process algebra family. Other well known formalisms include the Synchronous languages ESTEREL and LUSTRE [4].

In the industrial community, especially in the aerospace and automotive industries, the Unified Modeling Language (UML) [21] and the Architecture Analysis and Design Language (AADL) [28] have come to dominate notational conventions. At its onset, UML did not have formal semantics and remained a graphical language with limited support for automated analysis. Since its inception, many tools have defined their own semantics for UML, but the international standard [21] still does not contain a standard definition of the formal semantics. AADL contains formal semantics but is still in the early development stages, so it could not be completely evaluated. It is also unclear whether AADL can be used to specify low level functional behavior or if it is only applicable to architectural reasoning.

In the abstract state machine community, ASMs have been used to model specific examples of real-time systems [7, 14]. Some extensions have been proposed to the ASM theory to include timing characteristics [27] but the extensions make no mention of how time is to be specified (only the theoretical semantics are proposed) and do not address concurrency. The composition extensions for ASMs presented in this paper are based on the XASM language [1]. The XASM language does not include time or resource specification and only deals with single agent ASMs. The specification of resource consumption has not been addressed in the ASM community.

#### 3 The Abstract State Machine (ASM) Formalism

The abstract state machine formalism revolves around the concepts of an abstract machine and an abstract state. System behavior is specified as the computing steps of the abstract machine. A computing *step* is the atomic unit of computation, defined as a set of parallel updates made to global *state*. A *state* is defined as the values of all variables at a specific step. A machine *executes* a step by yielding a set of state updates. A *run*, potentially infinite, is a sequence of steps.

The following subsection presents the basic concepts of ASM theory. For a complete description of the theory of abstract state machines, the reader is referred to [8]. Our proposed extensions to the base theory are explained in section 4.

#### 3.1 Basic ASM Specification

The term *specification* is used to denote the complete document that results from the process of writing down a system design. This section introduces specifications that contain only a single abstract state machine, also known as *basic* or *single-agent* ASMs in the ASM community [8].

A basic abstract state machine specification is made up of two parts - an abstract state machine and an environment. The machine executes based on values in the environment and modifies values in the environment. The environment consists of two parts - the set of environment variables and the universe of types that variables can have. In the TASM language all variables are strongly typed. The machine consists of three parts - a set of monitored variables, a set of controlled variables, and a set of rules. The *monitored* variables are the variables in the environment that affect the machine execution. The *controlled* variables are the variables in the environment that the machine affects. The set of *rules* are named predicates, written in precondition-effect style, that express the state evolution logic.

Formally, a specification ASMSPEC is a pair:

$$ASMSPEC = \langle E, ASM \rangle$$

Where:

• E is the environment, which is a pair:

$$E = \langle EV, TU \rangle$$

Where:

- EV denotes the  $\it Environment \, \it Variables$ , a set of typed variables

- TU is the Type Universe, a set of types that includes:

- \* Reals:  $RVU = \mathbb{R}$

- \* Integers:  $NVU = \{..., -1, 0, 1, ...\}$

- \* Boolean constants:  $BVU = \{True, False\}$

- \* User-defined types: *UDVU*

- ASM is the machine, which is a triple:

$$ASM = \langle MV, CV, R \rangle$$

Where:

- MV is the set of *Monitored Variables* =  $\{mv \mid mv \in EV \text{ and } mv \text{ is read-only in } R\}$

- CV is the set of Controlled Variables =  $\{cv \mid cv \in EV \text{ and } cv \text{ is read-write in } R\}$

- R is the set of  $Rules = \{(n, r) \mid n \text{ is a name and } r \text{ is a rule of the form } if C then A \text{ where } C \text{ is an expression that evaluates to an element in } BVU \text{ and } A \text{ is an action} \}$

An action A is a sequence of one or more updates to environment variables, also called an *effect expression*, of the form v := vu where  $v \in CV$  and vu is an expression that evaluates to an element in the type of v.

Updates to environment variables are organized in *steps*, where each step corresponds to a *rule execution*. In the rest of this paper, the terms *step execution* and *rule execution* are used interchangeably. A rule is *enabled* if its guarding condition, C, evaluates to the boolean value True. The *update set* for the  $i^{th}$  step, denoted  $U_i$ , is defined as the collection of all updates to controlled variables for the step. An update set  $U_i$  will contain 0 or more pairs (cv, v) of assignments of values to controlled variables.

A run of a basic ASM is defined by a sequence of update sets.

#### 3.1.1 Light Switch Example Version 1

ENVIRONMENT:

A small example is presented to illustrate some of the features of the TASM language. Here the example shows a basic ASM specification describing the logic for switching a light on or off based on whether a switch is up or down. The specification is divided into sections, identified by capital letters followed by a colon. Comments in the specification are preceded by the escape sequence "//

```

USER-DEFINED TYPES:

light_status := {ON, OFF}

switch_status := {UP, DOWN}

VARIABLES:

light_status light

switch_status switch := DOWN

MAIN MACHINE:

MONITORED VARIABLES:

CONTROLLED VARIABLES:

liaht

RULES:

R1: Turn On

if light = OFF and switch = UP then

light := ON

R2: Turn Off

if light = ON and switch = DOWN then

light := OFF

```

A sample run with the initial environment ((light, OFF), (switch, UP)) yields one update set:

$$U_1 = ((light, ON))$$

After the step has finished executing, the environment becomes: ((light, ON), (switch, UP)).

# 4 The Timed Abstract State Machine Language

Here we describe the TASM language. We do this by introducing a series of modifications and extensions to the ASM formalism from Section 3.

#### **4.1** Time

The TASM approach to time specification is to specify the duration of a rule execution. In the TASM world, this means that each step will last a finite amount of time before an update set is applied to the environment. Syntactically, time gets specified for each rule in the form of an annotation. The specification of time can take the form of a single value t, or can be specified as an interval  $[t_{min},$  $t_{max}$ ]. The lack of a time annotation for a rule is assumed to mean t = 0. Semantically, a time annotation is interpreted as a value  $\in \mathbb{R}$ . If a time annotation is specified as an interval, the rule execution will last an amount  $t_i$ where  $t_i$  is taken randomly from the interval, which is interpreted as a closed interval on  $\mathbb{R}$ . The approach uses relative time between steps since each step will have a finite duration. The total time for a run of a given machine is simply the summation of the individual step times over the run. The time extensions are formally detailed in the following section, and the example from the previous section is extended to include time annotations.

#### 4.2 Resources

The specification of non-functional properties includes timing characteristics as well as resource consumption properties. A *resource* is defined as a global quantity that has a finite size. Power, memory, and communication bandwidth are examples of resources. Resources are used by the machine when the machine executes rules.

Because resources are global quantities, they are defined at the environment level. The environment E is extended to reflect the definition of resources:

$$E = \langle EV, TU, ER \rangle$$

Where:

- EV and TU remained unchanged from Section 3.1

- $\bullet$  ER is the set of named resources:

- $ER = \{(rn, rs) \mid rn \text{ is the resource name, and } rs \text{ is the resource size, a value } \in \mathbb{R} \}$

Similarly to time specification, syntactically, each rule specifies how much of a given resource it consumes. The specification of resource consumption takes the form of an annotation, where the resource usage is specified either as an interval or as a single value. The omission of a resource consumption annotation is assumed to mean zero resource consumption. The semantics of resource usage are assumed to be *volatile*, that is, usage lasts only through the step duration. For example, if a rule consumes

128 kiloBytes of memory, the total memory usage will be increased by 128 kiloBytes during the step duration and will be decreased by 128 kiloBytes after the update set has been applied to the environment.

Formally, a rule R of a machine ASM is extended to reflect time and resource annotations:

$$R = \langle n, t, RR, r \rangle$$

Where:

- n and r are defined in Section 3.1

- t denotes the duration of the rule execution and can be a single value  $\in \mathbb{R}$  or a closed interval on  $\mathbb{R}$

- RR is the set of resources used by the rule where each element is of the form (rr, ra) where  $rr \in ER$  is the resource name and ra is the resource amount consumed, specified either as a single value  $\in \mathbb{R}$  or as a closed interval on  $\mathbb{R}$

When a machine executes a step, the update set that is produced will contain the duration of the step, as well as the amounts of resources that were consumed during the step execution. We use the special symbol  $\bot$  to denote the absence of an annotation, for either a time annotation or a resource annotation. The role of the  $\bot$  symbol will become important in Section 4.3 and Section 4.4. Update sets are extended to include the duration of the step,  $t \in \mathbb{R}$   $\cup$   $\{\bot\}$  and a set of resource usage pairs  $rc = (rr, rac) \in RC$  where rr is the resource name and  $rac \in \mathbb{R} \cup \{\bot\}$  is a single value denoting the amount of resource usage for the step. If a resource is specified as an interval, rac is a value randomly selected from the interval.

The symbol  $TRU_i$  is used to denote the timed update set, with resource usages, of the  $i^{th}$  step of a machine, where  $t_i$  is the step duration,  $RC_i$  is the set of consumed resources, and  $U_i$  is the set of updates to variables from section 3.1:

$$TRU_i = (t_i, RC_i, U_i)$$

For the remainder of this paper, the term *update set* refers to an update set of the  $TRU_i$  form.

#### 4.2.1 Light Switch Example Version 2

The light switch example from the previous section is extended with time annotations and resource annotations. The sample resource is memory. For brevity, only the modified rules of the main machine are shown. The remainders of the specification are the same as in Version 1.

```

t := 6

memory := [128, 256]

if light = ON and switch = DOWN then

light := OFF

```

A sample run with the initial environment ((light, OFF), (switch, UP)) yields the following update set:

$$TRU_1 = (5, ((memory, 512)), ((light, ON)))$$

The duration of 5 time units was randomly selected from the interval [4, 10].

#### 4.3 Hierarchical Composition

The examples given so far have dealt only with a single sequential ASM. However, for more complex systems, structuring mechanisms are required to partition large specifications into smaller ones. The partitioning enables bottom-up or top-down construction of specifications and creates opportunities for reuse. The composition mechanisms included in the language are based on the XASM language [1]. In the XASM language, an ASM can use other ASMs in rule effects in two different ways - as a sub ASM or as a function ASM. A sub ASM is a machine that is used to structure specifications. A function ASM is a machine that takes a set of inputs and returns a single value as output, similarly to a function in programming languages. These two concepts enable abstraction of specifications by hiding details inside of auxiliary machines.

The definition of a sub ASM is similar to the previous definition of machine ASM:

$$SASM = \langle n, MV, CV, R \rangle$$

Where n is the machine name, unique in the specification, and other tuple members have the same definition as mentioned in previous sections. The execution and termination semantics of a sub ASM are different than those of a main ASM. When a sub ASM is invoked, one of its enabled rules is selected, it yields an update set, and it terminates.

The definition of a function ASM is slightly different. Instead of specifying monitored and controlled variables, a function ASM specifies the number and types of the inputs and the type of the output:

$$FASM = \langle n, IV, OV, R \rangle$$

Where:

- $\bullet$  *n* is the machine name, unique in the specification

- IV is a set of named inputs (ivn, it) where ivn is the input name, unique in IV, and  $it \in TU$  is its type.

- OV is a pair (ovn, ot) specifying the output where ovn is the name of the output and  $ot \in TU$  is its type

- R is the set of rules with the same definition as previously stated, but with the restriction that it only operates on variables in IV and OV.

A function ASM cannot modify the environment and must derive its output solely from its inputs. The only side-effect of a function ASM is time and resource consumption.

A specification, ASMSPEC, is extended to include the auxiliary ASMs:

$$ASMSPEC = \langle E, AASM, ASM \rangle$$

Where:

- E is the environment

- AASM is a set of auxiliary ASMs (both sub ASMs and function ASMs)

- ASM is the main machine

Semantically, hierarchical composition is achieved through the composition of update sets. A rule execution can utilize sub machines and function machines in its effect expression. Each effect expression produces an update set, and those update sets are composed together to yield a cumulative update set to be applied to the environment. To define the semantics of hierarchical composition, we utilize the semantic domain  $\mathbb{R} \cup \{\bot\}$  introduced in Section 4.2. The special value  $\bot$  is used to denote the absence of an annotation, for either a time annotation or a resource annotation.

We define two composition operators,  $\otimes$  and  $\oplus$ , to achieve hierarchical composition. The  $\otimes$  operator is used to perform the composition of update sets produced by effect expressions within the same rule:

$$TRU_1 \otimes TRU_2 = (t_1, RC_1, U_1) \otimes (t_2, RC_2, U_2)$$

=  $(t_1 \otimes t_2, RC_1 \otimes RC_2, U_1 \cup U_2)$

The  $\otimes$  operator is commutative and associative. The semantics of effect expressions within the same rule are that they happen in parallel. This means that the time annotations will be composed to reflect the duration of the longest update set:

$$t_1 \otimes t_2 = \begin{cases} t_1 & \text{if } t_2 = \bot \\ t_2 & \text{if } t_1 = \bot \\ max(t_1, t_2) & \text{otherwise} \end{cases}$$

The composition of resources also follows the semantics of parallel execution of effect expressions within the same rule. The  $\otimes$  operator is distributed over the set of resources:

$$RC_{1} \otimes RC_{2} = (rc_{11}, \dots, rc_{1n}) \otimes (rc_{21}, \dots, rc_{2n})$$

$$= (rc_{11} \otimes rc_{21}, \dots, rc_{1n} \otimes rc_{2n})$$

$$= ((rr_{11}, rac_{11}) \otimes (rr_{21}, rac_{21}), \dots, (rr_{1n}, rac_{1n}) \otimes (rr_{2n}, rac_{2n}))$$

$$= ((rr_{11}, rac_{11} \otimes rac_{21}), \dots ((rr_{1n}, rac_{1n} \otimes rac_{2n}))$$

In the TASM language, resources are assumed to be *additive*, that is, parallel consumption of amounts  $r_1$  and  $r_2$  of the same resource yields a total consumption  $r_1 + r_2$ :

$$rac_1 \otimes rac_2 = \begin{cases} rac_1 & \text{if } rac_2 = \bot \\ rac_2 & \text{if } rac_1 = \bot \\ rac_1 + rac_2 & \text{otherwise} \end{cases}$$

Intuitively, the cumulative duration of a rule effect will be the longest time of an individual effect, the resource consumption will be the summation of the consumptions from individual effects, and the cumulative updates to variables will be the union of the updates from individual effects.

The  $\oplus$  operator is used to perform composition of update sets between a *parent* machine and a *child* machine. A parent machine is defined as a machine that uses an auxiliary machine in at least one of its rules' effect expression. A child machine is defined as an auxiliary machine that is being used by another machine. For composition that involves a hierarchy of multiple levels, a machine can play both the role of parent and the role of child. An example of multi-level composition is given at the end of this Section. To define the operator, we use the subscript p to denote the update set generated by the parent machine, and the subscript c to denote the update set generated by the child machine:

$$TRU_p \oplus TRU_c = (t_p, RC_p, U_p) \oplus (t_c, RC_c, U_c)$$

$$= (t_p \oplus t_c, RC_p \oplus RC_c, U_p \cup U_c)$$

The  $\oplus$  operator is *not* commutative, but it is associative. The duration of the rule execution will be determined by the parent, if a time annotation exists in the parent. Otherwise, it will be determined by the child:

$$t_p \oplus t_c = \begin{cases} t_c & \text{if } t_p = \bot \\ t_p & \text{otherwise} \end{cases}$$

The distribution of the  $\oplus$  operator over the set of consumed resources is the same as for the  $\otimes$  operator:

$$RC_{p} \oplus RC_{c} = (rc_{p1}, \dots, rc_{pn}) \oplus (rc_{c1}, \dots, rc_{cn})$$

$$= (rc_{p1} \oplus rc_{c1}, \dots, rc_{pn} \oplus rc_{cn})$$

$$= ((rr_{p1}, rac_{p1}) \oplus (rr_{c1}, rac_{c1}), \dots, (rr_{pn}, rac_{pn}) \oplus (rr_{cn}, rac_{cn}))$$

$$= ((rr_{p1}, rac_{p1} \oplus rac_{c1}), \dots ((rr_{pn}, rac_{pn} \oplus rac_{cn}))$$

The resources consumed by the rule execution will be determined by the parent, if a resource annotation exists in the parent. Otherwise, it will be determined by the child:

$$rac_p \oplus rac_c = \begin{cases} rac_c & \text{if } rac_p = \bot \\ rac_p & \text{otherwise} \end{cases}$$

Intuitively, the composition between parent update sets and child update sets is such that the parent machine overrides the child machine. If the parent machine has annotations, those annotations override the annotations from child machines. If a parent machine doesn't have an annotation, then its behavior is defined by the annotations of the auxiliary machines it uses.

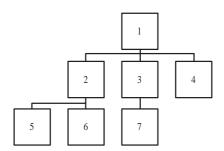

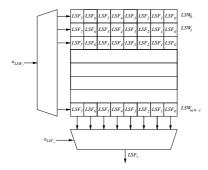

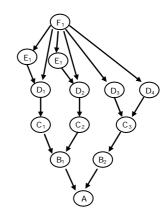

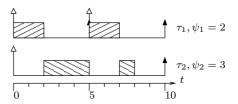

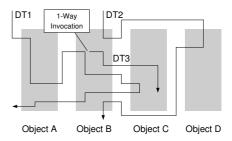

Figure 1 shows a hierarchy of machines for an sample rule execution. Each numbered square represents a machine. Machine "1" represents the rule of the main machine being executed; all other squares represent either sub machines or function machines used to derive the update set returned by the main machine. Machine "3" is an example of a machine that plays the role of parent (of machine "7") and child (of machine "1").

Figure 1. Hierarchical composition

Each machine generates an update set  $TRU_i$ , where i is the machine number. The derivation of the returned update set is done in a bottom-up fashion, where  $TRU_{ret}$  is the update set returned by the main machine:

$$TRU_{ret} = TRU_1 \oplus ( TRU_2 \oplus (TRU_5 \otimes TRU_6)) \otimes$$

$$(TRU_3 \oplus TRU_7) \otimes$$

$$TRU_4)$$

#### 4.3.1 Light Switch Example Version 3

The example from the previous sections is extended to illustrate the use of auxiliary ASMs. The example has been extended with a function ASM and a sub ASM.

```

FUNCTION MACHINE:

SUB MACHINE:

TURN_ON

TURN_OFF

MONITORED VARIABLES:

INPIIT VARIABLES:

switch status ss

switch

CONTROLLED VARIABLES:

OUTPUT VARIABLE:

light status ls

light

RULES:

RULES:

R1: Turn On

R1: Turn Off

t := [4, 10]

memory := 128

t := 6

if ss = UP then

ls := ON

if switch = DOWN then

light := OFF

R2: Else

R2: Else

else then

else then

```

The two modified rules of the main machine are shown below:

```

R1: Turn On

t := 1

if light = OFF and switch = UP then

```

```

light := TURN_ON(switch) //uses fASM

R2: Turn Off

memory := 1024

if light = ON and switch = DOWN then

TURN_OFF() //uses sASM

```

The first step of two sample runs are shown below:

- Initial environment: ((light, OFF), (switch, UP)) Update set: (1, ((memory, 128)), ((light, ON)))

- Initial environment: ((light, ON), (switch, DOWN)) Update set: (6, ((memory, 1024)), ((light, OFF)))

The first sample run invokes the function ASM and obtains the step duration from the main ASM definition and the resource consumption from the function ASM. The second sample run obtains the variable updates and rule duration from the sub ASM and the resource consumption from the main ASM.

#### 4.4 Parallel Composition

To enable specification of multiple parallel activities in a system, the TASM language allows parallel composition of multiple abstract state machines. Parallel composition is enabled through the definition of multiple top-level machines, called main machines. Formally, the specification ASMSPEC is extended to include a set of main machines MASM as opposed to the single main machine ASM for basic ASM specifications:

$$ASMSPEC = \langle E, AASM, MASM \rangle$$

Where:

- *E* is the environment

- AASM is a set of auxiliary ASMs (both sub ASMs and function ASMs)

- MASM is a set of main machines ASM that execute in parallel

The definition of a main machine ASM is the same as from previous sections. Other definitions also remain unchanged.

The semantics of parallel composition regards the synchronization of the main machines with respect to the global progression of time. We define tb, the global time of a run, as a monotonically increasing function over  $\mathbb{R}$ . Machines execute steps that last a finite amount of time, expressed through the duration  $t_i$  of the produced update set. The time of generation,  $tg_i$ , of an update set is the value of tb when the update set is generated. The time of application,  $ta_i$ , of an update set for a given machine is defined as  $tg_i + t_i$ , that is, the value of tb when the update set will be applied. A machine whose update set, generated at global time  $tg_p$ , lasts  $t_p$  will be busy until  $tb = tg_p + t_p$ . While it is busy, the machine cannot perform other steps. In the meantime, other machines who are not busy are free to perform steps. This informal definition gives

rise to update sets no longer constrained by step number, but constrained by time. Parallel composition, combined with time annotations, enables the specification of both synchronous and asynchronous systems.

We define the operator  $\odot$  for parallel composition of update sets. For a set of update sets  $TRU_i$  generated during the same step by i different main machines:

$$\begin{split} TRU_1 \odot TRU_2 &= (t_1, RC_1, U_1) \odot (t_2, RC_2, U_2) \\ &= \begin{cases} (t_1, RC_1 \odot RC_2, U_1) & \text{if } t_1 < t_2 \\ (t_2, RC_1 \odot RC_2, U_2) & \text{if } t_1 > t_2 \\ (t_1, RC_1 \odot RC_2, U_1 \cup U_2) & \text{if } t_1 = t_2 \end{cases} \end{split}$$

The operator  $\odot$  is both commutative and associative. The distribution of the  $\odot$  operator over the set of resource consumptions is the same as for the  $\otimes$  and  $\oplus$  operators:

$$RC_{1} \odot RC_{2} = (rc_{11}, \dots, rc_{1n}) \odot (rc_{21}, \dots, rc_{2n})$$

$$= (rc_{11} \odot rc_{21}, \dots, rc_{1n} \odot rc_{2n})$$

$$= ((rr_{11}, rac_{11}) \odot (rr_{21}, rac_{21}), \dots, (rr_{1n}, rac_{1n}) \odot (rr_{2n}, rac_{2n}))$$

$$= ((rr_{11}, rac_{11} \odot rac_{21}), \dots ((rr_{1n}, rac_{1n} \odot rac_{2n}))$$

The parallel composition of resources is assumed to be additive, as in the case of hierarchical composition using the  $\otimes$  operator:

$$rac_1 \odot rac_2 = \begin{cases} rac_1 & \text{if } rac_2 = \bot \\ rac_2 & \text{if } rac_1 = \bot \\ rac_1 + rac_2 & \text{otherwise} \end{cases}$$

At each global step of the simulation, a list of pending update sets are kept in an ordered list, sorted by time of application. At each global step of the simulation, the update set at the front of the list is composed in parallel with other update sets, using the ⊙ operator and the resulting update set is applied to the environment. Once an update set is applied to the environment, the step is completed and the global time of the simulation progresses according to the duration of the applied update set.

To enable communication between different machines, the TASM language provides synchronization channels, in the style of the Calculus of Communication Systems (CCS) [20]. A *synchronization channel* is defined as a global object, uniquely identified by its name, that is used by two machines to synchronize. When using a communication channel, one machine plays the role of *sender* and the other machine plays the role of *receiver*. The syntax for using a communication channel is based on CCS. For an example communication channel named x, a sender would use x! to send a notification and a receiver would use x? to receive a notification. For more details on the features of the TASM language, the reader is referred to [22].

| Component | Action         | Duration | Power |

|-----------|----------------|----------|-------|

| Feed      | Move block     | 5        | 500   |

| Deposit   | Move block     | 5        | 500   |

| Robot     | Rotate 30°     | 1        | 1000  |

| Robot     | Drop a block   | 1        | 1000  |

| Robot     | Pickup a block | 1        | 1000  |

| Press     | Stamp a block  | 11       | 1500  |

**Table 1. Durative actions**

#### 5 Production Cell Example

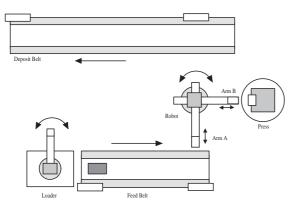

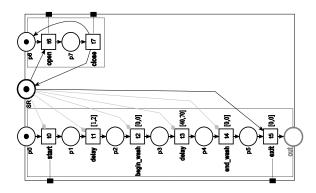

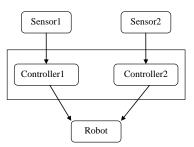

This section illustrates the features of the TASM language through the modeling of a more substantial example, the production cell case study [19]. The production cell consists of a series of components that need to be coordinated to achieve a common goal. The purpose of the production cell system is to stamp blocks. Blocks come into the system from the *loader*, which puts the block on the *feed belt*. Once the block reaches the end of the feed belt, the *robot* can pick up the block and insert it into the *press*, where the block is stamped. Once the block has been stamped, the robot can pick up the block from the press and unload it on the *deposit belt*, at which point the stamped block is carried out of the system. The schematic view of the production cell system is shown in Figure 2.

Figure 2. Top view of the production cell

All components operate concurrently and must be synchronized to achieve the system's goal. The robot has two arms, arm A and arm B, which move in tandem and can pick up and drop blocks in parallel. For example, the robot can drop a block in the press while picking up a block from the feed. A *controller* coordinates the actions of the system by sending commands to the robot.

Some simplifications and extensions have been made to the original problem definition [19]. For example, the elevating rotatory table has been omitted. The original example has been extended to reflect the reality that certain actions are *durative*, that is, they last a finite amount of time. The example has also been extended to include a resource, *power consumption*. The list of durative actions, with their power consumptions, are shown in Table 1.

All other actions are assumed to be instantaneous and are assumed to consume no power. In the TASM model, each component of the production cell is modeled as a main machine. The model also contains a main machine for the controller. Sub machines and function machines are used, mostly to structure the actions of the robot. The robot waits for a command from the controller and then executes that command before waiting for another command. Listing 1 shows the first rule of the submachine that updates the robot's position. Listing 2 shows the second rule of the main machine Feed, which carries a block from the loader to the robot. The time annotation specifies the amount of time that it takes for the block to travel from the loader to the robot.

#### Listing 1 Rule 1 of submachine UPDATE\_POSITION

Due to lack of space, other rules and other component specifications are omitted; the complete list of machines is shown in Table 2.

#### Listing 2 Rule 2 of main machine Feed

We use these two listings to illustrate the semantics of parallel composition. For a partial initial environment ((feed\_belt, loaded), (command, rotatecw), (robot\_angle, 30), (armapos, intransit), (armbpos, intransit)) with the two main machines Feed and Robot with associated auxiliary machines, two update sets are generated by the main machines:

```

\begin{split} TRU_{Feed,1} = &(5, ((power, 500)), ((feed\_block, available)) \\ TRU_{Robot,1} = &(1, ((power, 1000)), ((robot\_angle, 0.0), \\ &(armapos, at feed), (armbpos, at press))) \end{split}

```

The parallel composition of these two update sets yields the environment described below. For brevity, only the environment variables whose values are changed are shown. The time t denotes the global simulation time:

- t < 1: (((power, 1500)),  $\emptyset$ )

- t = 1: (((power, 1500)), ((feed\_block, available)))

| Name                   | Type     | Purpose                                |

|------------------------|----------|----------------------------------------|

| Controller             | Main     | Sends commands to the robot            |

| Loader                 | Main     | Loads blocks onto the feed belt        |

| Feed                   | Main     | Carries blocks from the loader         |

| Robot                  | Main     | Processes commands                     |

| Press                  | Main     | Stamps blocks                          |

| Deposit                | Main     | Carries blocks out of the system       |

| allEmpty               | Function | Determines whether the robot is loaded |

| armPosition            | Function | Returns the position of an arm         |

| rotateClockwise        | Function | Changes the robot angle by +30°        |

| rotateCounterClockwise | Function | Changes the robot angle by -30°        |

| DROP_ARM_A             | Sub      | Drop a block from arm A                |

| DROP_ARM_B             | Sub      | Drop a block from arm B                |

| DROP_BLOCKS            | Sub      | Invokes the drop submachines           |

| EXECUTE_COMMAND        | Sub      | Executes a command                     |

| PICK_UP_ARM_A          | Sub      | Picks up a block with arm A            |

| PICK_UP_ARM_B          | Sub      | Picks up a block with arm B            |

| PICK_UP_BLOCKS         | Sub      | Invokes the pick up submachines        |

| UPDATE_POSITION        | Sub      | Updates the angle of the robot         |

Table 2. List of all machines used in the production cell model

- 1 < t < 5: (((power, 1000)),  $\emptyset$ )

- t = 5: (((power, 1000)), ((robot\_angle, 0.0), (armapos, at feed), (armbpos, at press))

- t > 5: (((power, 0)),  $\emptyset$ )

The complete model, including all the components, was run for a scenario where the loader fed a total of 5 blocks into the system, with the initial state shown in Figure 2. It took a total of 219 simulation steps and 103 time units for all 5 blocks to go through the system, given the controller strategy.

#### 6 Conclusion and Future Work

The contributions of this paper span two different areas. On the theoretical side, the paper presents extensions to the ASM formalism to facilitate the specification of real-time systems. The specification includes both functional and non-functional properties, integrated into a unified formalism. The incorporation of timing, resource, and functional behavior into a single language fills an important need of the real-time system community [9, 17]. This is achieved both for basic TASM specifications and for the composition of specifications. The resulting formalism keeps the same theoretical foundations of ASM theory but is better suited for modeling real-time systems because of the support to explicitly state resource consumption and timing behavior. On the practical side, this paper defines a formalism that has the potential of being both formal and usable. By basing the formalism on the theory of abstract state machines, the purpose is to bring the stated benefits of using abstract state machines to the designers of reactive real-time systems.

On the theoretical side, verification techniques and test-case generation techniques are currently being surveyed and studied to understand how these capabilities could be applied to the proposed language. Preliminary results suggest leveraging existing verification tools (e.g., UPPAAL [18]) by defining semantic preserving formal mappings between the TASM language and the formalisms of existing verification tools [25]. On the practical side, the TASM language is the first step towards a framework for validation and verification of high-integrity embedded systems [24]. The language will serve as the basis for the framework and an associated toolset to write and analyze real-time system specifications is being developed [23]. The TASM language will be incorporated into a suite of tools that will be used to verify timing and resource consumption behavior of embedded real-time systems [26].

#### References

- M. Anlauff. XASM An Extensible, Component-Based Abstract State Machines Language. In Abstract State Machines - ASM 2000, International Workshop on Abstract State Machines. TIK-Report 87, 2000.

- [2] J. Bergstra, A. Ponse, and S. Smolka. A Handbook of Process Algebra. North-Holland, 2001.

- [3] M. Bernardo and F. Corradini. Formal Methods for the Design of Real-Time Systems. Springer-Verlag, 2004.

- [4] G. Berry. The Essence of ESTEREL. In *Proof, Language and Interaction: Essays in Honour of Robin Milner*. MIT Press, 2000.

- [5] B. W. Boehm. Software Engineering Economics. Prentice-Hall, 1981.

- [6] E. Börger. Why Use Evolving Algebras for Hardware and Software Engineering? In Proceedings of the 22nd Seminar on Current Trends in Theory and Practice of Informatics, SOFSEM '95, volume 1012 of LNCS. Springer-Verlag, 1995.

- [7] E. Börger, Y. Gurevich, and D. Rosenzweig. The Bakery Algorithm: Yet Another Specification and Verification. In Specification and Validation Methods. Oxford University Press, 1995.

- [8] E. Börger and R. Stärk. Abstract State Machines. Springer-Verlag, 2003.

- [9] B. Bouyssounouse and J. Sifakis. Embedded Systems Design: The ARTIST Roadmap for Research and Development. Springer, 2005.

- [10] J. P. Bowen and M. G. Hinchey. Ten Commandments of Formal Methods. *IEEE Computers*, 28(4), April 1994.

- [11] A. Cerone and A. Maggiolo-Schettini. Time-based Expressivity of Time Petri Nets for System Specification. In *Theoretical Computer Science*, volume 216. Springer-Verlag, 1999.

- [12] A. K. Cheng. Real-Time Systems: Schedulability, Analysis, and Verification. John Wiley and Sons, 2003.

- [13] E. M. Clarke and J. Wing. Formal Methods: State of the Art and Future Directions. ACM Computing Surveys, 28(3), 1996.

- [14] J. Cohen and A. Slissenko. On Verification of Refinements of Asynchronous Timed Distributed Algorithms. In *International Workshop on Abstract State Machines*. Springer-Verlag, 2000.

- [15] D. Harel and A. Naamad. The STATEMATE Semantics of Statecharts. ACM Transactions on Software Engineering

- and Methodology, 5(4), 1996.

- [16] T. A. Henzinger, Z. Manna, and A. Pnueli. Timed Transition Systems. In *Real-Time: Theory in Practice, REX Workshop*, pages 226–251, 1991.

- [17] A. Jantsch and I. Sander. Models of Computation and Languages for Embedded System Design. *IEE Proceedings Computers and Digital Techniques*, 152(2), March 2005.

- [18] K. G. Larsen, P. Pettersson, and W. Yi. UPPAAL in a Nutshell. *International Journal on Software Tools for Technol*ogy Transfer, 1:134–152, 1997.

- [19] C. Lewerentz and T. Lindner. Production Cell: A Comparative Study in Formal Specification and Verification. In KORSO Methods, Languages, and Tools for the Construction of Correct Software, 1995.

- [20] R. Milner. Communication and Concurrency. Prentice Hall, 1980.

- [21] Object Management Group, Inc. Unified Modeling Language: Superstrucure. Version 2.0. OMG Specification, August 2005.

- [22] M. Ouimet. The TASM Language Reference Manual, Version 1.1. Available from http://esl.mit.edu/tasm, November 2006.

- [23] M. Ouimet, G. Berteau, and K. Lundqvist. Modeling an Electronic Throttle Controller using the Timed Abstract State Machine Language and Toolset. In *Proceedings* of the Satellite Events of the 2006 MoDELS Conference, LNCS, October 2006.

- [24] M. Ouimet and K. Lundqvist. The Hi-Five Framework and the Timed Abstract State Machine Language. In *Proceedings of the 27th IEEE Real-Time Systems Symposium Work in Progress Session*, December 2006.

- [25] M. Ouimet and K. Lundqvist. Automated Verification of Completeness and Consistency of Abstract State Machine Specifications using a SAT Solver. In *Proceedings of the* 3rd International Workshop on Model-Based Testing (MBT '07), Satellite Workshop of ETAPS '07, April 2007.

- [26] M. Ouimet and K. Lundqvist. Verifying Execution Time using the TASM Toolset and UPPAAL, January 2007. Technical Report ESL-TIK-000212, Embedded Systems Laboratory, Massachusetts Institute of Technology.

- [27] H. Rust. Using Abstract State Machines: Using the Hypperreals for Describing Continuous Changes in a Discrete Notation. In Abstract State Machines – ASM 2000. Springer-Verlag, March 2000.

- [28] SAE Aerospace. Architecture Analysis & Design Language Standard. SAE Publication AS506, 2004.

- [29] J. M. Wing. A Specifier's Introduction to Formal Methods. *IEEE Computers*, 23(9), 1990.

### **Extended Real-Time LOTOS for Preemptive Systems Verification**

Tarek Sadani<sup>(1)(2)</sup>, P. de Saqui-Sannes<sup>(1)(2)</sup>, J-P. Courtiat<sup>(1)</sup>

<sup>1</sup>LAAS-CNRS, 7 avenue du colonel Roche, 31077 Toulouse Cedex 04, France

<sup>2</sup>ENSICA, 1 place Emile Blouin, 31056 Toulouse Cedex 05, France

tsadani@ensica.fr; desaqui@ensica.fr; courtiat@laas.fr

Fax: +33 5 61 61 86 88

#### **Abstract**

Real-time systems not only interact with their environment and hopefully deliver their expected outputs on time. Unlike transformational systems, they may be interrupted at any time while keeping the capacity to restart later on without loosing their state information. Therefore, a real-time system specification language should include a suspend/resume capability. In this paper, we propose to extend the timed process algebra RT-LOTOS with a suspend/resume operator. Extended RT-LOTOS specifications are translated to Stopwatch Time Petri nets that may be analyzed using the TINA tool. We define an RT-LOTOS to SwTPN translation pattern. A formal proof is included. Case studies show the interest of our proposal for preemptive systems specification and verification.

#### 1 Introduction

A wealth of formal models have been proposed in the literature to describe and analyze real-time systems. Few of them enable explicit description of suspend/resume operations. Examples include Stopwatch Time Petri nets[6] and Stopwatch automata[11]. As a timed process algebra, RT-LOTOS[13] also makes it possible to describe important features of real-time systems (e.g., parallelism, reaction to stimuli from the environment, delay, temporal indeterminism). RT-LOTOS supports a disrupt operator which allows a process Q to suspend another process P for ever. Suspension in RT-LOTOS is hence reduced to unrecoverable abortion. Clearly, RT-LOTOS misses resume capabilities. This weakness is inherited from (untimed) LOTOS. In [15] it is shown that LOTOS misses some mechanisms to deal with suspend/resume behaviors. This paper's contribution is to extend RT-LOTOS with a suspend/resume operator. The proposed extension is given a formal semantics without disturbing the semantic model of RT-LOTOS. It is worth to be noticed that discussion goes beyond language aspects. The challenge is to have extended RT-LOTOS specifications effectively model checked. We propose to translate RT-LOTOS specifications into Stopwatch Time Petri nets (SwTPN)[6].

The latter are rigorously analyzed using TINA[8], the Time Petri net analyzer developed by LAAS-CNRS. The paper is organized as follows. Section 2 presents RT-LOTOS. Section 3 explains the expected benefits of adding a suspend/resume operator to RT-LOTOS. Section 4 presents SwTPN. Section 5 discusses RT-LOTOS to SwTPN translation, it includes a formal proof. Section 6 presents three examples. Section 7 surveys related work. Section 8 concludes the paper and outlines future work.

#### 2 RT-LOTOS

Real-Time LOTOS, or RT-LOTOS for short, is a timed extension of the ISO-based formal description technique LOTOS (Language of Temporal Ordering of Specification)[20]. LOTOS relies on the CCS process algebra and inherits a multiple rendez-vous mechanism from Hoare's CSP. RT-LOTOS enables explicit and semantically well-founded description of temporal mechanisms. Three generic temporal operators have been added to LOTOS: First, a deterministic delay expressed by the delay operator. For instance, delay(d) makes it possible to delay a process P for a certain amount of time d. Second, a non-deterministic delay expressed by the latency operator. For instance, latency(l) makes it possible to delay a process for a value that is non-deterministically selected in [0, 1]. Its usefulness and efficiency have been demonstrated in [12]. The third temporal operator is a time-limited offer associated with an action. For instance,  $g\{t\}$  allows one to limit the amount of time allocated to offer an action a.

The following processes *P* and *PL* illustrate the use of the three temporal operators of RT-LOTOS.

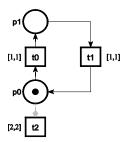

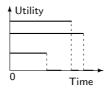

Process P starts with a 2 time units delay. Once the delay expires, action a is offered to the environment during 5 time units. If the process's environment does not synchronize on a before this deadline, a time violation occurs and the process transforms into stop. Process PL differs from P, for it contains a latency operator. Action a is delayed by a minimum delay of 2 units of time and a maximum

delay of 8 units of time (in case the *latency* goes to its maximum value). From the environment's point of view, if the latency lasts l time units, the process behaves like  $delay(2+l)a\{5-l\}$  (cf. the left part of Figure 1). Of course, if the duration of the latency goes beyond 5 units of time, a temporal violation occurs and process PL transforms into stop(cf. the right part of Figure 1).

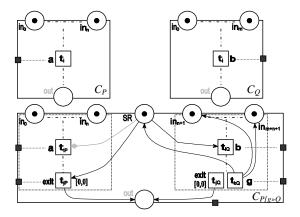

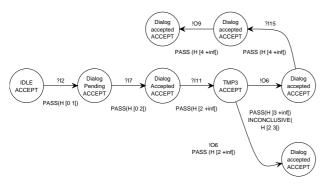

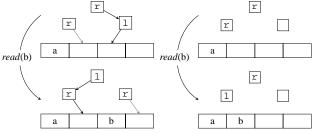

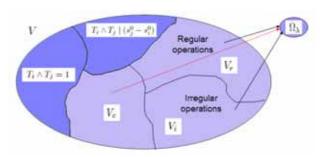

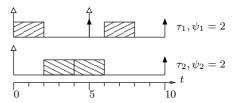

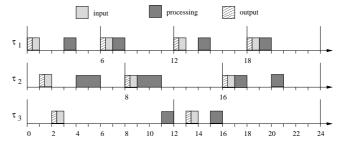

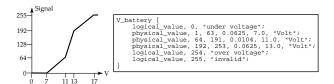

Figure 1. Delay, latency and Limited offering

The originality and interest of the latency operator is more obvious when one combines that operator with the hiding operator. In LOTOS, hiding allows one to transform an external observable action into an internal one. In RT-LOTOS, hiding has the form of a renaming operator which renames action a into i(a). In most timed extensions of LOTOS, hiding implies urgency. It thus removes any time indeterminism inherent to the limited time offering. In RT-LOTOS, a hidden action is urgent as soon as it is no longer delayed by some latency operator. Let us, e.g., consider the RT-LOTOS behavior hide a in PL where action a is hidden in process PL. If l is the duration of the latency, i(a) will necessarily occur at date 2 + l, if l < 5. (cf. Figure 2). But, if (l > 5), a temporal violation occurs (similarly to the situation where action a was an observable action).

Figure 2. Hiding in RT-LOTOS

# 3 An RT-LOTOS Suspend/Resume operator

#### 3.1 Rationale

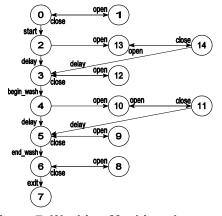

Is RT-LOTOS well-suited to specify that a process execution may be stopped and resumed later on? To answer that question, let us consider the behavior of a simplified washing machine. It is made up of two processes named Machine and Cover, respectively.

```

process Machine[start,b_wash,e_wash]:exit:=

start; b_wash; e_wash; exit

endproc

process Cover[open, close]: exit:=

open; close; Cover[open,close]

endproc

```

Machine may be suspended by Cover at any time during its execution, and resumed after the completion of each Cover instance (each instance of Cover yields an 'open; close' action sequence).

The RT-LOTOS disrupt [> operator is not appropriate to

model that kind of behavior. Machine[...][> Cover[...] allows Machine to be suspended, but not to be resumed. An infinite sequence of 'open; close' actions will follow Machine's interruption.

The use of the parallel composition operator ||| would not be more appropriate, since the resulting interleaving of actions in Machine[...] ||| Cover[...], does not ensure that Cover will terminate before Machine is resumed<sup>1</sup>.

Another solution is to adopt a state-oriented style. Using the choice [] and the enabling  $\gg$  operators, we explicitly define all the possible suspending points in Machine (actions are indivisible). For this sake the behavior of Machine is changed as follows:

```

Process Machine2[start,b_wash,e_wash,open,close]

:exit

((start; exit)

[](Cover[open, close] >> (start; exit)))

>>((b_wash; exit)

[](Cover[open, close] >> (b_wash; exit)))

>>((e_wash; exit)

[](Cover[open, close] >> (e_wash; exit)))

endproc

```

The definition of Cover has also to be changed to a non recursive one. This is to avoid an infinite sequence of Cover's actions and to ensure Machine actually resumes. However this 'contortion' lowers the readability and compositionality of the specification (although Machine is a simple sequence of actions) and allows only three times the 'open; close' sequence.

Let us now consider a timed extension of the washing machine.

```

Hide b_wash, e_wash in

process Machine[start,b_wash, e_wash]: exit:=

start;delay(1,2)b_wash;delay(40,70)e_wash;exit

endproc

```

After the occurrence of start,  $b\_wash$  is delayed by a 1 up to 2 units delay. Washing takes between 40 and 70 units of time. Actions  $b\_wash$  and  $e\_wash$  are internalized and therefore urgent. In this revisited specification, it is impossible to define all the suspension points because we are considering a dense time model. Moreover using a specification technique based on the modification of the suspended behavior (Machine2) is no longer possible; it does not preserve the timing constraints in the original Machine process. Let us consider the following behavior expressed in state-oriented fashion:

```

(delay(1,2)b_wash; exit)

[](Cover[open,close]>>delay(1,2)b_wash; exit)

```

The choice offered between the two alternatives is resolved in the interaction with the environment. Cover is executed if the environment offers open, unless  $b\_wash$  is executed (after a delay between 1 and 2 units of time). Until the choice is resolved the two alternatives age similarly. Let us now suppose the environment offers action open after 1 unit of time, which leads to the following execution:

```

\begin{array}{l} (\text{delay}(1,2)b\_wash...) \ [] \ (\text{Cover[open, close}] \gg ...) \xrightarrow{\rightarrow} \\ (\text{delay}(0,1)b\_wash...) \ [] \ (\text{Cover[open, close}] \gg ...) \xrightarrow{Cover[...]} \\ (\text{delay}(1,2)b\_wash; \text{ exit)} \end{array}

```

<sup>&</sup>lt;sup>1</sup>||| may be seen as a non deterministic solution to model coroutines.

After the elapsing of 1 unit of time,  $b\_wash$  must be enabled at most after 1 time unit. In the resulting behavior, after the completion of process Cover,  $b\_wash$  has to wait for a delay between 1 and 2 units of time, whereas 1 unit of time of this delay has already elapsed (the timing context is not restored).

# 3.2 Syntax and Semantics of the Suspend/Resume operator

Section 3.1 pointed out that RT-LOTOS lacks a mechanism for a modular description, of a process *P* whose temporal evolution can be suspended and then resumed at the same point.

To remedy to this situation we propose to add a suspend/resume operator to RT-LOTOS. It is represented by  $[g\gg (g \text{ being the gate used to resume}), \text{ which is a mix between the disrupt }[> \text{ and the enabling }\gg \text{ operators (we extend }[> \text{ to handle resumption)}. $P[g\gg Q$ \text{ models the possible suspension of main behavior }P$ by $Q$, $Q$ is executed till it terminates or executes action $g$, in the last case, the control returns to process $P$, in the same point it has been suspended. This special gate $g$ is not fixed syntactically in the operator, and the user is free to use any gate name.$

Special attention is provided to give the proposed extension a simple semantics, which further suits abstract reasoning. We follow on the recommendation made in [5] on providing preemption primitives at first-class level and with full orthogonality to other concurrency and communication primitives. The behavior (P[g>Q) is formally defined using Plotkin-style structural semantics (SOS rules).

We introduce the following semantic operator  $\ll$ g]. The latter expresses that P has been suspended by Q. This operator appears only at the semantic level. It may not be used in RT-LOTOS specifications.

In the following  $G_P$  denotes the set of observable and hidden gates of P.

1)

$$\frac{P \xrightarrow{a} P'}{P[g \gg Q \xrightarrow{a} P'[g \gg Q)} a \in G_P \setminus \{\text{exit}\}$$

2)

$$\frac{P \xrightarrow{exit} P'}{P[g \gg Q \xrightarrow{exit} P'}$$

3)

$$\frac{Q \xrightarrow{a} Q'}{P[g \gg Q \xrightarrow{a} P \ll g] Q'}$$

4)

$$\frac{Q \xrightarrow{a} Q'}{P \ll g] Q \xrightarrow{a} P \ll g] Q'} a \in G_Q \setminus \{g\}$$

5)

$$\frac{Q \xrightarrow{b} Q'}{P \ll g] Q \xrightarrow{b} P \ll g] Q'}$$

6)

$$\frac{Q \xrightarrow{g} Q'}{P \ll g] Q \xrightarrow{g} P \parallel g \gg Q'}$$

7)

$$\frac{P \xrightarrow{b} P', Q \xrightarrow{b} Q'}{P[g \gg Q \xrightarrow{b} P'] g \gg Q'}$$

Rule 1 defines the normal execution of P. It says that after any action a of P, Q is still given the chance to suspend P (Q is still active).

Rule 2 says that if P has successfully completed its

execution, then Q can no longer be executed.

Rule 3 defines control passing between P and Q at the occurrence of one of the first actions of Q.

Rule 4 and rule 5 say that Q is the only active behavior. The suspended behavior P can not perform any action (rule 4). Further, it cannot age (rule 5).

Rule 7 says that regarding time, [g] behaves as [> (the aging of P induces the aging Q).

One could think that we are missing some rule, to define the behavior of  $P \ll g]Q$  when Q terminates successfully, in order to get rid of the suspended behavior P, but the termination of Q is supported by rule 4 where the suspended behavior is kept (this is not a problem, since Q cannot do any action after its termination, therefore P cannot be resumed). Moreover, if this termination is captured by an enabling, all the whole behavior  $(P \ll g]Q)$  is forgotten.

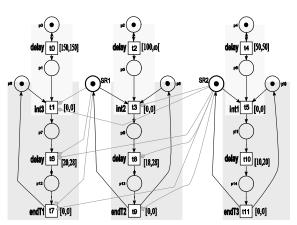

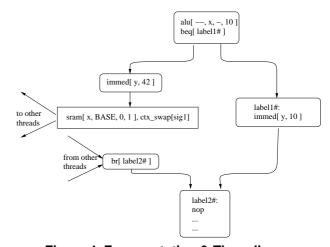

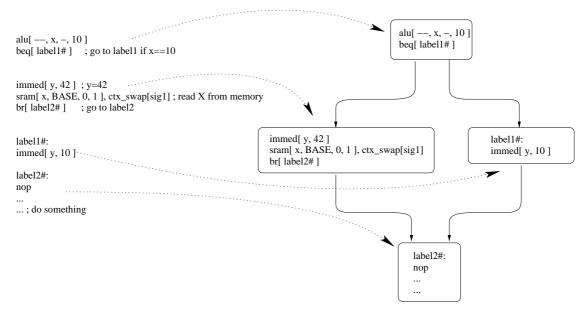

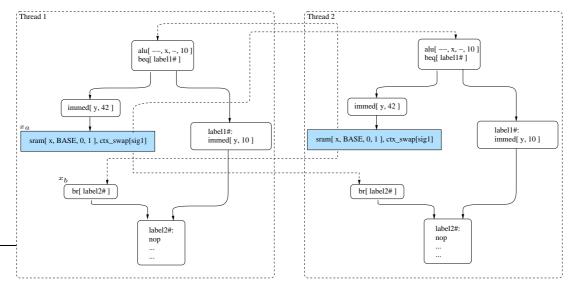

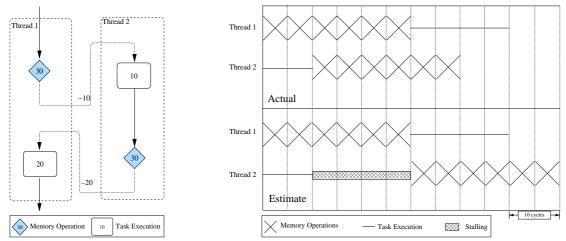

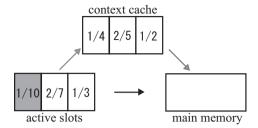

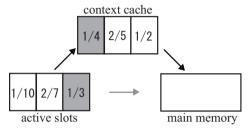

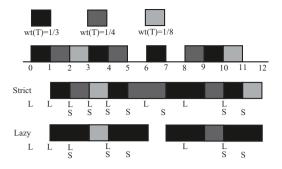

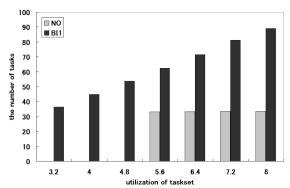

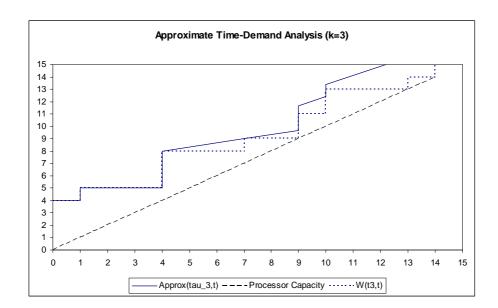

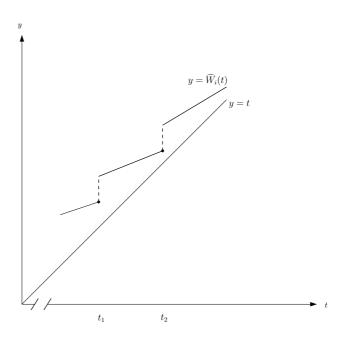

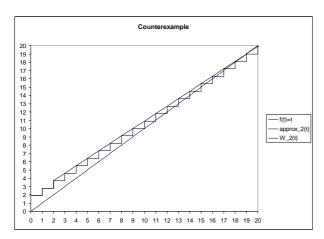

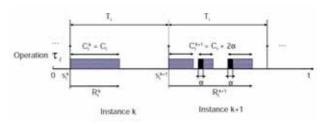

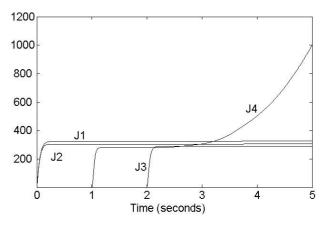

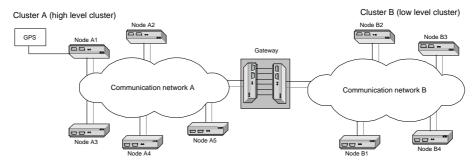

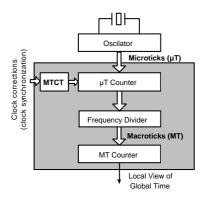

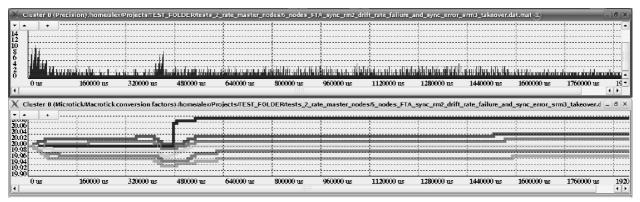

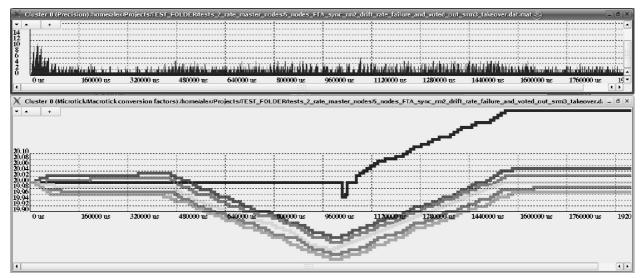

#### 4 Time Petri Nets with Stopwatches